(1) dry etch를 사용하는 이유

: wet etch는 isotropic profile 때문에 미세공정에 부적합.

∴ 고집적화된 최신 공정은 일부를 제외하고 대부분 dry etch 방식 사용.

(2) dry etch 종류

1) non-plasma 방식: 반응성 gas의 혼합으로 자연스런 화학반응 이용.

2) plasma 방식 (현실에서는 대부분 plasma 방식 사용)

- chemical etching

- physical etching (=sputtering)

- chemical physical etching (가장 많이 사용되는 방식)

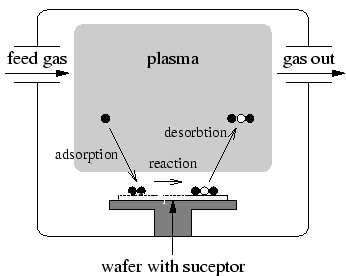

①plasma chemical etching

- plasma 내 radical을 이용하는 방식. (radical: 중성의 비활성 원자와 분자의 가스 상태)

- radical이 wafer의 대상물질과 화학반응을 통해 휘발성 부산물을 만들며 etch → isotropic → 미세패턴X

- gas 이용 → 반응속도↓ → etch rate↓

- 높은 압력과 down stream batch 구조를 통해 개선.

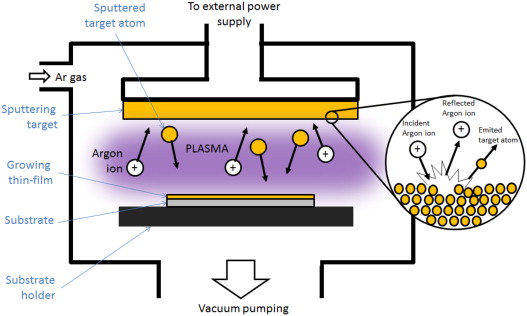

②plasma physical etching (sputtering)

- plasma 내 양이온을 target에 물리적으로 충돌시켜 뜯어내는 방식(순수하게 물리적).

- 진공 chamber(∵양이온 운동 원활하게)에서 single wafer 방식으로 진행.

- 주로 Ar gas 사용(∵불활성 원소로 중성원자 상태에서 화학적 반응 일으키지 않기 때문).

- anisotropic etching이 가능하지만 etch rate가 느림.

- selcectivity↓ → 하부 막질에 damage 발생 가능.

③plasma chemical & physical etching (=RIE)

- 측벽은 chemical etching만 → 등방성이지만 etch rate↓

- 하부는 chemical&physical etching 동시 진행 → 양이온이 부산물 빨리 탈출하게 해줌

→ radical의 화학반응 도와줌 → etch rate↑ - etch rate 차이로 인해 anisotropic etching 가능.

- Ar, CF4 gas 이용. CF3 & F는 chemical etching. Ar+ & CF3+는 physical etching.

④protective ion enhanced etching

- RIE의 부족한 이방성을 보완.

- etch구조에 chemical etching을 억제하는 보호막(passivation film) 증착

→ 하부 영역의 보호막은 physical etching으로 사라짐. 측벽의 보호막만 남음

→ anisotropic 성질↑ - 보호막 증착을 위한 별도 gas 필요 (ex. Si 나 SiO2 RIE etching에 CHF3)

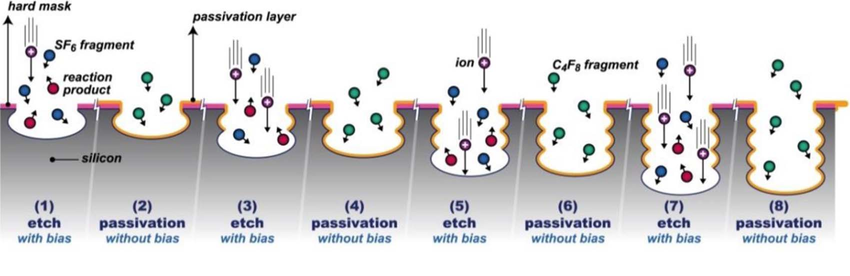

⑤deep RIE (=BOSCH)

- etching과 보호막 증착을 연속해서 반복 → 더 높은 수준의 anisotropic.

- 시간과 비용은 더 들지만, 높은 AR 구조 구현가능.

- SF6 plasma로 Si etching → CFx plasma로 보호막 증착 → 다시 SF6 plasma로 etching → 보호막 증착 → 반복.

<참고문헌> 이창훈, 반도체 소소제공, 더인 출판사, 2019, pp.155-163.

'반도체 > 반도체 공정' 카테고리의 다른 글

| 12. cleaning 공정(1) (목적, 방식) (0) | 2020.06.05 |

|---|---|

| 11. Plasma (정의, 생성원리, 활용원리) (0) | 2020.06.02 |

| 9. Wet etch의 방식과 etchant (1) | 2020.06.01 |

| 8. Etch 공정의 정의와 parameter, 종류 (0) | 2020.06.01 |

| 7. Photo 공정의 개선(2) (기법 개선) (0) | 2020.06.01 |